2

# **DRAWINGS**

Please amend original FIG. 1 to now be referenced as "FIG. 1A" as shown in the attached Annotated Marked-Up Drawings, with changes indicated in pink highlight. Also please amend the drawings to include FIG. 1B. Attached are Replacement Sheets for the now-referenced FIG. 1A and FIG. 1B.

#### **REMARKS**

Claims 2-16 and 18-25 were pending when last examined. All pending claims are shown in the detailed listing above.

## **Drawings**

Applicants have amended original FIG. 1 to now be referenced as "FIG. 1A."

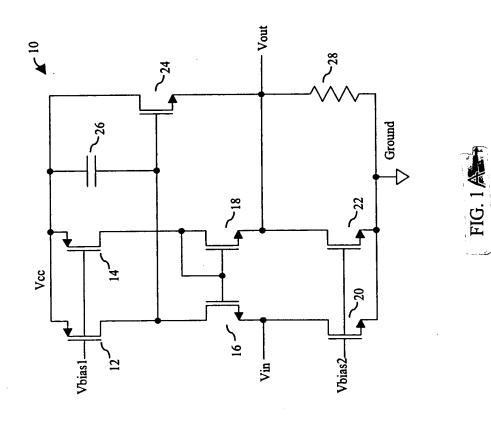

Applicants have included a new drawing FIG. 1B, which Applicants respectfully submit is fully supported by the Application as filed and does not add any new matter. In particular, FIG. 1B is substantially similar to original FIG. 1 in the Application, but replaces the transistors 12, 14, 20, and 22 with current sources as described at paragraphs [0013] and [0015] of the Application. Paragraph [0013] of the specification states: "During operation, transistors 12 and 14 may provide relatively constant current and, as such, can be considered or alternatively implemented as current sources." Likewise, Paragraph [0015] of the specification states, "During operation, transistors 20 and 22 may provide relatively constant current and, as such, can be considered or alternatively implemented as current sources."

## Specification

Applicants have amended paragraphs [0007] and [0011] to reflect the changes to the drawing figures and to correct a minor informality.

Applicants have amended the paragraphs on page 5 of the specification to correct minor informalities in the paragraph numbering. The number for the first paragraph [0001] has been changed to "[0019]" and the number for the second paragraph [0001] has been changed to "[0020]," which is clearly appropriate since these two paragraphs fall between paragraph [0018] (starting at the bottom of page 4) and paragraph [0021] (starting at the bottom of page 5). Applicants have also amended the paragraph [0019] to correct a minor typographical error.

The Examiner objects to the disclosure. According to the Examiner:

[T]he disclosure "In precision buffer circuit 10, in some embodiments, only transistors 16, 18, and 24 are conducting signal currents. The remaining transistors--i.e., transistors 12, 14, 18, 20 and 22 are conducting only bias currents, thus operating to provide relatively constant current" in page 5, paragraph [0001] is misleading. Figure 1 of the present application show that if transistors 12, 14, 20, 22 do not conduct signal currents, transistors 16, 18 and 24 will not conduct any current also because transistors 16 and 18 are isolated from supply source (Vcc and ground). Note that because transistors 12, 16, 20 and 14, 18, 22 are connected in cascode between supply voltage (Vcc) and ground, transistors 12, 16, 20 conduct a same current and transistors 14, 18, 22 conduct a same current.

Office Action, p. 2. Applicants respectfully traverse.

The Examiner misunderstands what constitutes a "signal current." In particular, not every current which flows through a transistor is a "signal current." A signal current is one in which the magnitude can change in order to provide or indicate a signal. In the specification as filed, the currents flowing through transistors 16, 18, and 24 change during operation in response to changes in the input signal Vin. See pages 4-5 of the Application. For example, the specification states, "The slew rate  $\Delta V/\Delta t$  may have a value equal to the quiescent current flowing in transistor 16 divided by the value of capacitor 26. Accordingly, less current flows through transistor 16. This causes the voltage at the gate of transistor 24 to increase, and thus, more current flows through transistor 24." Thus, the currents flowing through transistors 16, 18, and 24 as described in the specification are signal currents.

In contrast, any current flowing through a transistor which is unchanging cannot be a "signal current"; otherwise, how could such current provide or indicate a signal. In the specification, the current flowing through transistors 12, 14, 20, and 22 are unchanging. The specification states: "During operation, transistors 12 and 14 may provide relatively constant current and, as such, can be considered or alternatively implemented as current sources." Paragraph [0013]. Likewise, the specification states, "During operation, transistors 20 and 22 may provide relatively constant current and, as such, can be considered or alternatively

implemented as current sources." Paragraph [0015]. As such, the currents flowing through transistors 12, 14, 20, and 22 as described in the specification are *not* signal currents. But these transistors 12, 14, 20, and 22 do conduct unchanging *bias* currents.

In light of the above, the disclosure of the Application at page 5 is accurate, and not misleading.

# Claim Rejections - 35 USC § 112

Claims 18-20 stand rejected under 35 U.S.C. § 112, second paragraph, as being indefinite for failing to particularly point out and distinctly claim the subject matter which applicant regards as the invention. According to the Examiner, "Regarding claim 18, the recitation 'at most three transistors operable to provide signal currents' on line 4 is indefinite because it is misdescriptive. Figure 1 of the present application shows that there are more than 3 transistors (12, 14, 16, 18, 20, 22) in the circuit that provide signal currents." Applicants respectfully traverse.

As explained above, the specification accurately describes that only transistors 16, 18, and 24 in Figure 1 of the Application provide signal currents. Transistors 12, 14, 20, and 22 do not provide any signal currents, but instead provide unchanging *bias* currents.

Furthermore, Applicants have included new drawing FIG. 1B which makes clear that in one embodiment only three transistors 16, 18, and 24 are conducting *signal* currents, as recited in claims 18-20. As discussed above, FIG. 1B is fully supported by the Application as filed and does not add any new matter.

Thus, Claims 18-20 are not indefinite, and the rejection of these claims under 35 U.S.C. § 112, second paragraph should be withdrawn.

### Claim Rejections - 35 USC § 102

Claims 18-20 stand rejected under 35 U.S.C. § 102(b) as being anticipated by Xu (US 6,066,985). Applicants respectfully traverse.

Claim 18 recites, *inter alia*, "A buffer circuit comprising... at most three transistors operable to provide signal currents; wherein the output signal is fed back to the two matched transistors to counter any change in the input signal appearing at the input terminal; a first current source connected to the one of the two matched transistors; and a second current source connected to the other of the two matched transistors." Nowhere in Xu are such limitations disclosed or taught.

According to the Examiner, "Regarding claims 18-20, figure 2 of Xu shows a buffer circuit comprising...first and second current sources (P107, P108)...." Applicants respectfully disagree. The element P107 in Xu is not a current source. It is a diodeconnected transistor, and as such, does not source current. Thus, Xu does not anticipate claim 18.

For at least the reasons discussed above, Applicants respectfully request that the rejection of claim 18 under 35 U.S.C. § 102(b) be withdrawn and this claim be allowed. Furthermore, because claims 19 and 20 depend from claim 18 and include further limitations, the Applicants respectfully request that the rejection of these dependent claims under 35 U.S.C. § 102(b) also be withdrawn and that claims 19 and 20 be allowed.

### Response to Arguments

The Examiner does not find the Applicants' arguments in the Response of September 22, 2006 to be persuasive. The Examiner states:

Applicant's arguments filed 09-26-06 have been fully considered but they are not persuasive. In the Remarks, the Applicant argues that the recitation "at most three transistors operable to provide signal currents" in

16

claim 18 is fully supported and described in the specification, page 5, paragraph [0001]. This disclosure is misleading. Figure 1 of the present application show that if transistors 12, 14, 20, 22 do not conduct signal currents, transistor 16, 18 and 24 will not conduct any current also because transistors 16 and 18 are isolated from supply source (Vcc and ground).

Office Action, p. 3..

The Examiner's response to Applicants' arguments is mooted for all of the reasons discussed above.

### Allowable Subject Matter

Applicants appreciate the Examiner's allowance of Claims 2-16 and 21-25.

# **CONCLUSION**

Applicants respectfully request that the pending claims be allowed and the case passed to issue. Should the Examiner wish to discuss the Application, it is requested that the Examiner contact the undersigned at (415) 772-7428.

Certificate of Mailing

I hereby certify that this correspondence is being deposited with the United States Postal Service on the date shown below with sufficient postage as first class mail in an envelope addressed to: Commissioner for Patents, P.O. Box 1450, Alexandria, VA 22313-1450.

Date

Signature

March 30, 2007

SIDLEY AUSTIN LLP 555 California Street, Suite 2000 San Francisco, CA 94104-1715 Respectfully submitted,

By:

Philip W. Woo Attorney of Record Registration No. 39,880

PWW/rp

"High-Precision Buffer Circuit" Inventors: Steven O. Smith et al. Appln. Serial No.: 10/757,115 Atty. Docket No.: 24317/82951 Sheet 1 of 3

Annotated Marked-Up Drawing